Summary

In modern warfare, decisions are driven by information.

That information can come in the form of thousands of sensors providing information, surveillance, and reconnaissance (ISR) data; logistics/supply-chain and personnel performance measurements; or a host of other sources and formats. The ability to exploit this data to understand and predict the world around us is an asymmetric advantage for the Department of Defense (DoD).

Utilizing this data relies on computational algorithms running at a huge scale. Today, developers are limited in their ability to run these algorithms efficiently because they generally have to trade the efficiency of their algorithms with that of the available hardware architecture implementations. To combat this challenge, one solution is to design and fabricate application specific integrated circuits (ASICs) — customized hardware designed to maximize the runtime efficiency of a specific algorithm. However, ASICs typically cost hundreds of millions of dollars and take many years to develop.

Once developed, they can perform exactly one class of computation because they were designed and specialized for specific application tasks. Because these systems are so specifically tailored and costly, their creation is often limited to the highest priority algorithms. For problems that cannot afford this level of investment, compute efficiency is sacrificed by implementing solutions such as software on general-purpose processors or field programmable gate arrays (FPGAs). Often, this results in application implementations that are thousands of times worse than optimal.

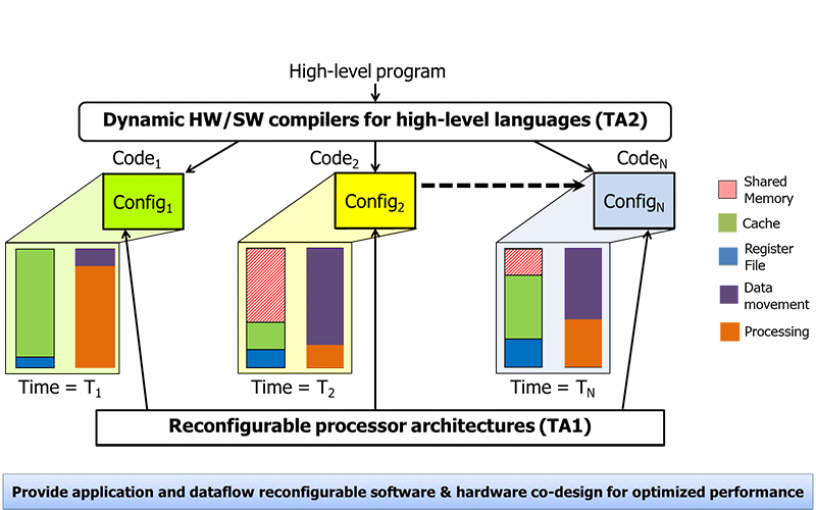

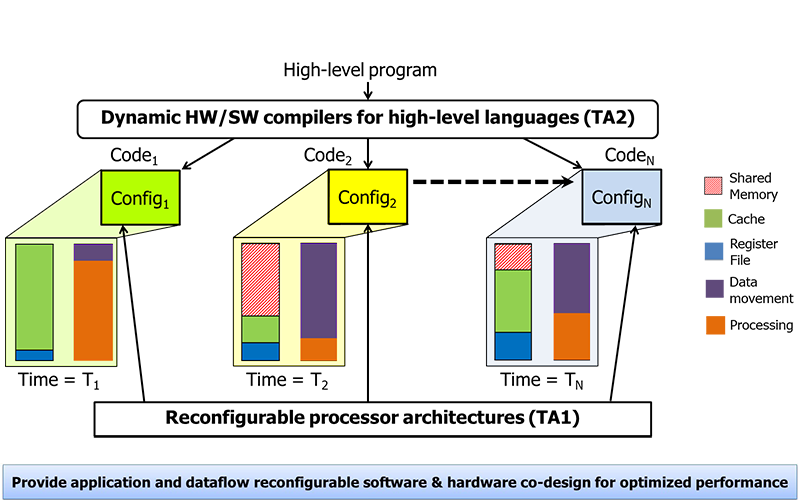

The goal of the Software Define Hardware (SDH) program is to build runtime-reconfigurable hardware and software that enables near ASIC performance without sacrificing programmability for data-intensive algorithms. Under the program, data-intensive algorithms are defined as machine learning and data science algorithms that process large volumes of data and are characterized by their usage of intense linear algebra, graph search operations, and their associated data-transformation operators.

The SDH program aims to create hardware/software systems that allow data-intensive algorithms to run at near ASIC efficiency without the cost, development time, or single application limitations associated with ASICs. If successful, SDH will result in the ability to develop and run data-intensive, data-exploitation algorithms at very low cost, and, consequently, enable pervasive use of big-data solutions for a wide range of DoD applications including ISR, predictive logistics, decision support, and beyond.

SDH Program Concept and Structure

The SDH program will create malleable hardware/software architectures that, unlike ASICs, allow an application to defer hardware configuration to runtime. SDH will enable 1) the optimization of code and hardware dynamically when input data change, and 2) the reuse of hardware for new problems and new algorithms to solve existing problems. In order to accomplish these objectives, SDH targets very fast hardware reconfiguration speeds and dynamic compilation. If successful, SDH will be able to take advantage of data-dependent optimizations that even today’s ASICs cannot exploit.

The SDH program will measure compute efficiency (in terms of giga-operations per watt (GOPs/Watt)). By the end of the program, it is expected that SDH systems to be at efficiencies within 5X of ASICs and 500-1000X better than CPU implementations with the same programmability as current NumPy/Python implementations.

This program is now complete

This content is available for reference purposes. This page is no longer maintained.