Summary

The explosive growth in mobile and telecommunication markets has pushed the semiconductor industry toward integration of digital, analog, and mixed-signal blocks into system-on-chip (SoC) solutions.

Advanced silicon (Si) complementary metal oxide semiconductor (CMOS) technology has enabled this integration, but has also led to a rise in costs associated with design and processing. Driven by aggressive digital CMOS scaling for high-volume products, Intellectual Property (IP) reuse has emerged as a tool to help lower design costs associated with advanced SoCs.

The monolithic nature of state-of-the-art SoCs is not always acceptable for Department of Defense (DoD) or other low-volume applications due to factors such as high initial prototype costs and requirements for alternative material sets. To enhance overall system flexibility and reduce design time for next-generation products, the Common Heterogeneous Integration and Intellectual Property (IP) Reuse Strategies (CHIPS) program seeks to establish a new paradigm in IP reuse.

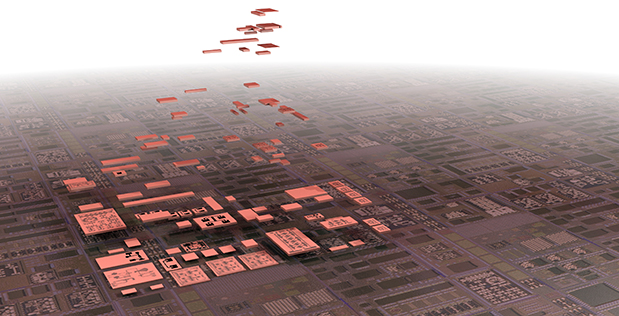

The vision of CHIPS is an ecosystem of discrete modular, reusable IP blocks, which can be assembled into a system using existing and emerging integration technologies. Modularity and reusability of IP blocks will require electrical and physical interface standards to be widely adopted by the community supporting the CHIPS ecosystem. Therefore, the CHIPS program will develop the design tools and integration standards required to demonstrate modular integrated circuit (IC) designs that leverage the best of DoD and commercial designs and technologies.

This program is now complete.

This content is available for reference purposes. This page is no longer maintained.